Luckily, the software creates most of the test bench itself.

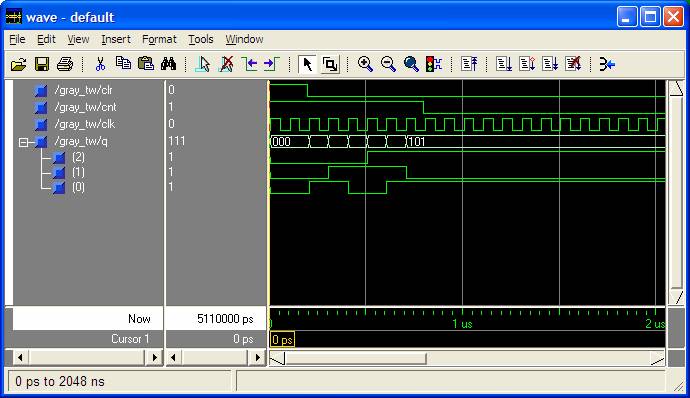

In order to verify what I just said, a test bench is generated with the aid of the Xilinx ISE 13.1 software. According to my limited knowledge (and according to other programmers) these are the code for frequency dividing and pwm: Frequency divider: Described with my own words, the frequency is divided by a 5000 factor which yields to a new frequency of 10000Hz (0.1ms. The reset signal is an essential part in any digital system and its function in this component is to restart the counter. Hi: Im trying to control a servomotor HS-645MG with the Altera FPGA DE0 using VHDL.

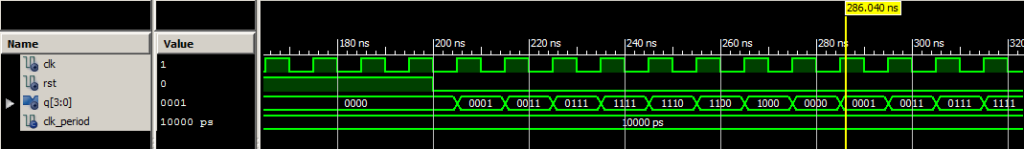

A counter can be implemented implicitly with a Register Inference. Since the counter begins at zero, the superior limit is 125000 - 1. Implementing Counters (VHDL) Counters use sequential logic to count clock pulses. Why 124999 and not 250000? A clock signal is a square wave with a 50% of duty cycle (same time active and inactive) for this case, 125000 cycles active and 125000 cycles inactive. The frequency_divider process, lines 16 to 28, generates the 200Hz signal by using a counter from 1 to 124999. The inputs and outputs of the system are declared between the lines 4 through 10. Lines 1 and 2 are equivalent to the C/C++ #include or the Python import statements. Signal counter : integer range 0 to 124999 := 0 įrequency_divider: process (reset, clk_in) begin

0 Comments

Leave a Reply. |

RSS Feed

RSS Feed